Maparea memoriei

Chip-urile de memorie

Chip-urile au, în general, următorii pini:

- pinii de adrese

- pinii de date

- pin de chip-enable (numit și chip-select sau output-enable)

- pin de Read/Write (dacă memoria poate fi suprascrisă)

În practică chip-urile de memorie pot avea și alți pini (Reset, Write-Protect, pini de alimentare, etc.), dar în cadrul exercițiilor ignorăm aceste detalii.

Arhitectura din chip-ul de memorie

Un chip de memorie are un număr de adrese folosibile (ex: 1024 de adrese), iar la fiecare adresă stochează date (pe 8 biți, pe 16 biți, etc. în funcție de specificații).

Numărul de pini de adresare este determinat de numărul de adrese folosibile din acel chip, considerând ca adresele folosibile din chip sunt numerotate de la zero (ex: un chip cu 1024 de adrese foloseste 10 pini de adresa, notați A[0] - A[9]).

De asemenea, numărul de pini de date este determinat de dimensiunea celulei de stocare (ex: dacă chip-ul stochează câte 16 biți la fiecare adresa de memorie, va avea 16 pini de date, notați D[0-15]).

Ieșirile de date sunt active doar dacă pinul de Chip-Enable este activat. Altfel, ieșirile sunt lăsate “în aer” (floating, deconectate).

Atenție! Un chip poate stoca 2KB de date sub forma de 1024 de adrese x 16 biți.

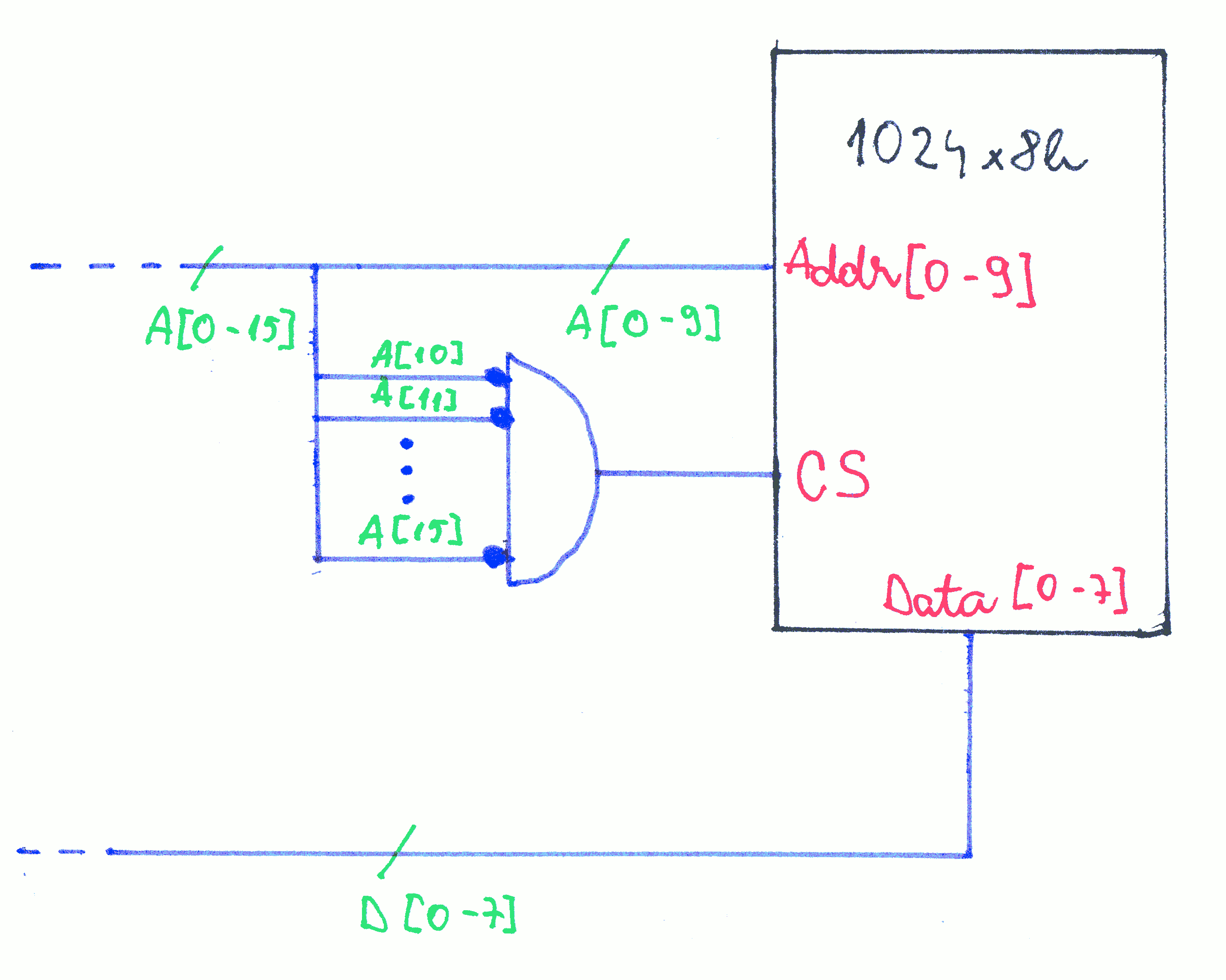

Exemplul 1

Task: Conectarea unui chip 1024x8b într-o arhitectură cu adrese pe 16 biți și date pe 8 biți, pentru a acoperi adresele între 0x0000 și 0x03FF.

Împărțirea spațiului de adrese:

| A[15] | A[14] | A[13] | A[12] | A[11] | A[10] | A[9] | A[8] | A[7] | A[6] | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | Comentariu |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a chip-ului |

| 0 | 0 | 0 | 0 | 0 | 0 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a chip-ului |

Observăm ca chip-ul este folosit doar atunci când liniile de adresă A[10-15] sunt zero.

Condiția de chip-select este !A[15] & !A[14] & !A[13] & !A[12] & !A[11] & !A[10].

Celelalte linii de adresă (A[0-9]) sunt legate direct la chip-ul de memorie.

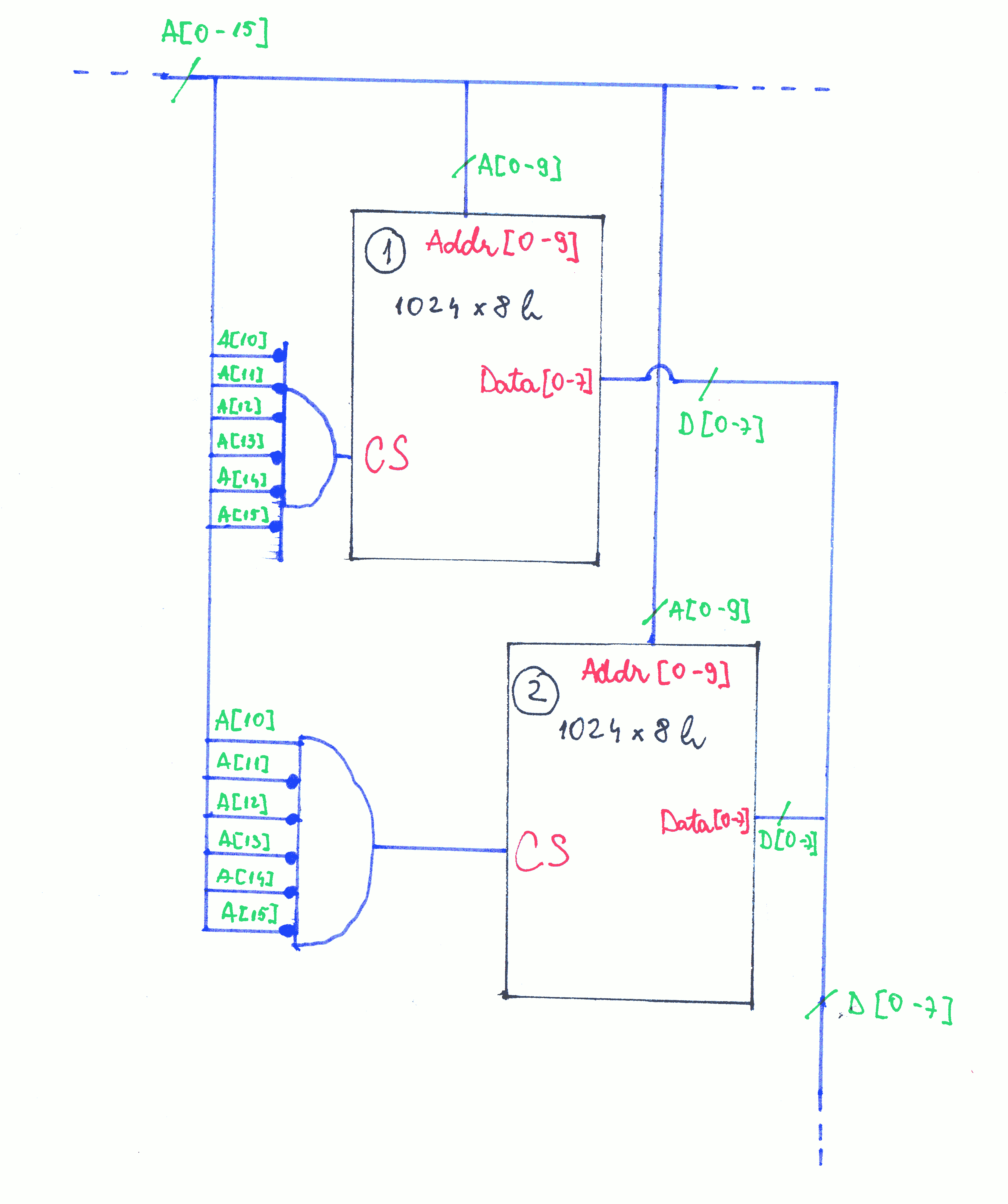

Exemplul 2

Task: Conectarea a două chip-uri 1024x8b cu adrese consecutive, la începutul spațiului de adrese a unei arhitecturi cu date pe 8 biți și adrese pe 16 biți.

Asta înseamnă să facem din nou tabelul cu împărțirea spațiului de adrese:

| A[15] | A[14] | A[13] | A[12] | A[11] | A[10] | A[9] | A[8] | A[7] | A[6] | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | Comentariu |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a chip-ului 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a chip-ului 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a chip-ului 2 |

| 0 | 0 | 0 | 0 | 0 | 1 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a chip-ului 2 |

Pe baza tabelului deducem că:

- condiția de chip-select pentru chip-ul 1 este

!A[15] & !A[14] & !A[13] & !A[12] & !A[11] & !A[10]. - condiția de chip-select pentru chip-ul 2 este

!A[15] & !A[14] & !A[13] & !A[12] & !A[11] & A[10].

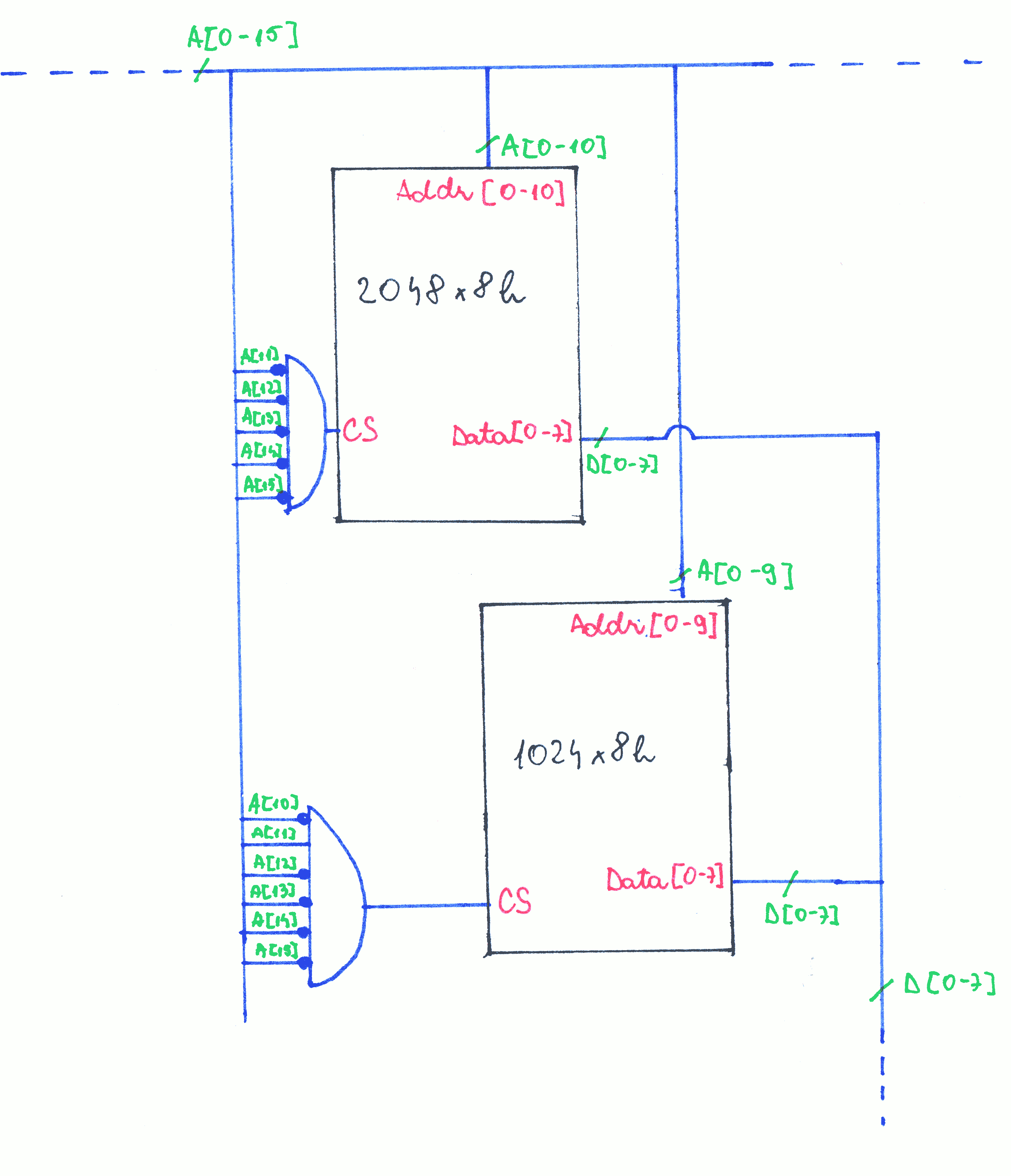

Exemplul 3

Task: Conectarea unui chip 2048x8b urmat de un chip 1024x8b la începutul spațiului de adrese a unei arhitecturi cu date pe 8 biți și adrese pe 16 biți.

Asta înseamnă să facem din nou tabelul cu împărțirea spațiului de adrese:

| A[15] | A[14] | A[13] | A[12] | A[11] | A[10] | A[9] | A[8] | A[7] | A[6] | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | Comentariu |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a chip-ului 2048x8b |

| 0 | 0 | 0 | 0 | 0 | … | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a chip-ului 2048x8b |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a chip-ului 1024x8b |

| 0 | 0 | 0 | 0 | 1 | 0 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a chip-ului 1024x8b |

Pe baza tabelului deducem că:

- condiția de chip-select pentru chip-ul

2048x8beste!A[15] & !A[14] & !A[13] & !A[12] & !A[11]. - condiția de chip-select pentru chip-ul

1024x8beste!A[15] & !A[14] & !A[13] & !A[12] & A[11] & !A[10].

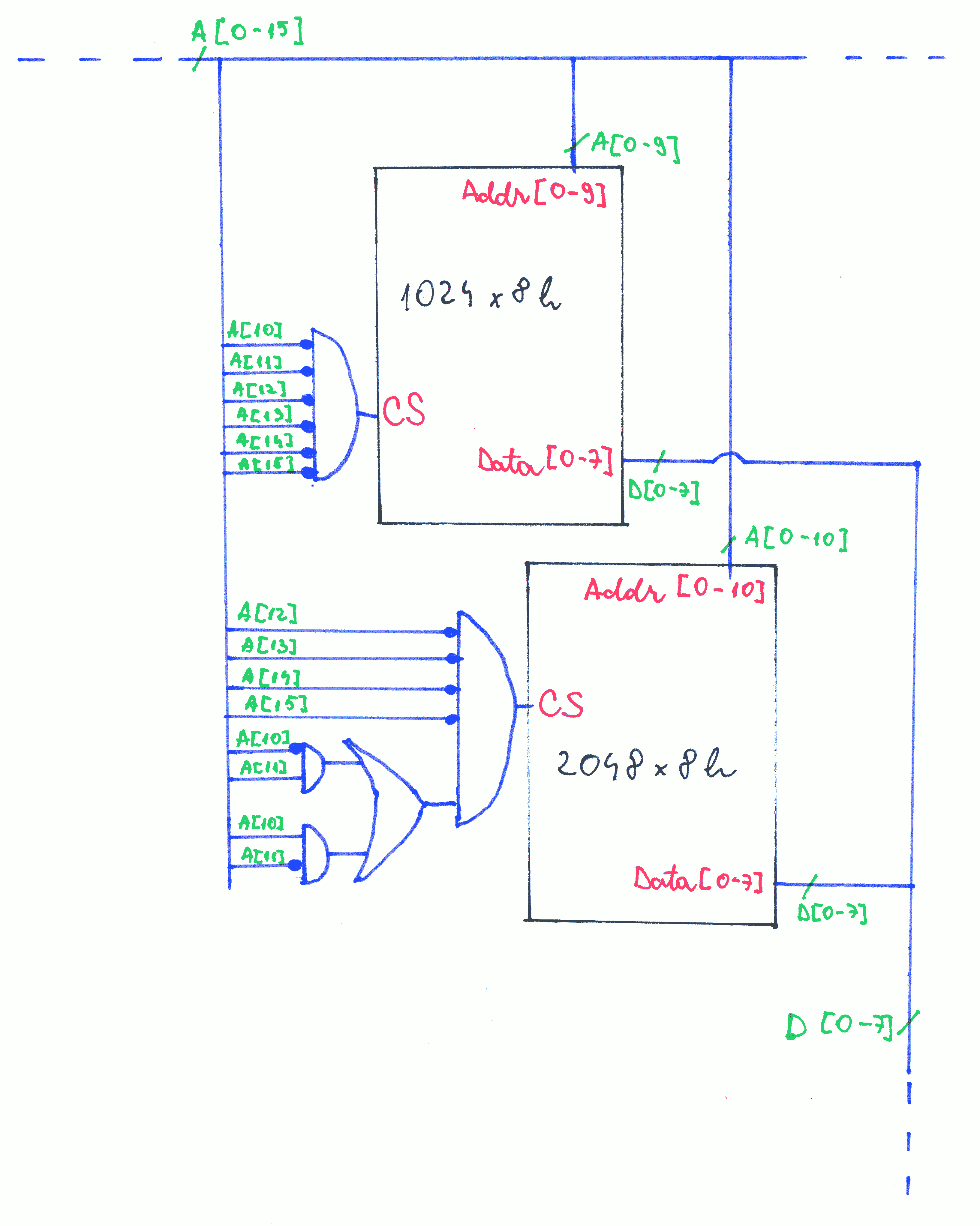

Exemplul 4

Task: Conectarea unui chip 1024x8b urmat de un chip 2048x8b la începutul spațiului de adrese a unei arhitecturi cu date pe 8 biți și adrese pe 16 biți.

Asta înseamnă să facem din nou tabelul cu împărțirea spațiului de adrese:

| A[15] | A[14] | A[13] | A[12] | A[11] | A[10] | A[9] | A[8] | A[7] | A[6] | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | Comentariu |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a chip-ului 1024x8b |

| 0 | 0 | 0 | 0 | 0 | 0 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a chip-ului 1024x8b |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a chip-ului 2048x8b |

| 0 | 0 | 0 | 0 | 0 | 1 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 0 | 1 | 0 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a chip-ului 2048x8b |

Pe baza tabelului deducem că:

- condiția de chip-select pentru chip-ul

1024x8beste!A[15] & !A[14] & !A[13] & !A[12] & !A[11] & !A[10]. - condiția de chip-select pentru chip-ul

2048x8beste!A[15] & !A[14] & !A[13] & !A[12] & ((!A[11] & A[10]) | (A[11] & !A[10])).

Trebuie observat că adresa 0b0000.0100.0000.0000 “văzută” de placa de bază ca fiind prima adresă din al doilea chip este interpretată ca fiind 0b100.0000.0000 din perspectiva chip-ului de memorie (nu este prima adresă, ci este interpretată ca fiind la mijlocul spațiului de memorie, spațiu cuprins între 0b000.0000.0000 și 0b111.1111.1111). Acest lucru nu ne încurcă, întrucât folosim toate adresele de memorie suportate de chip.

Exemplul 5

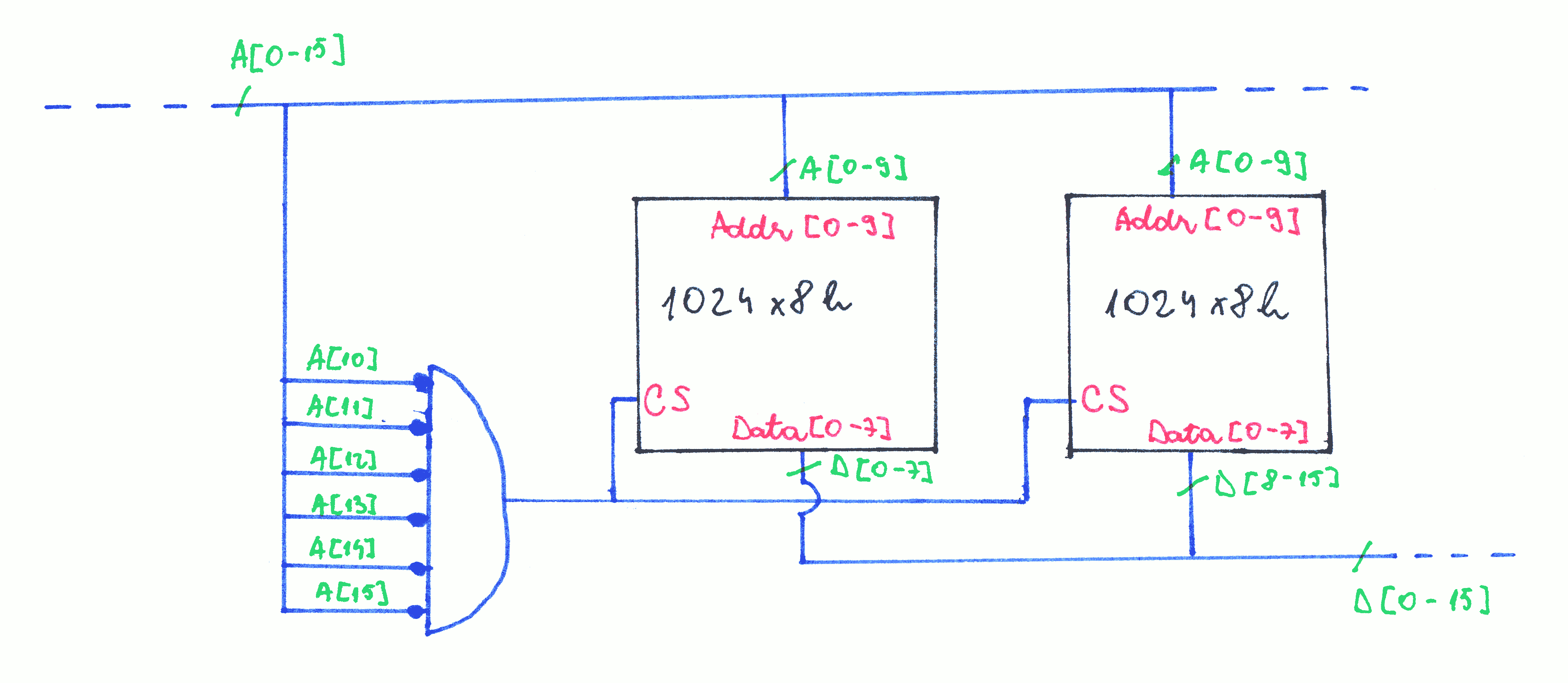

Task: Conectarea folosind chip-uri 1024x8b într-o arhitectură cu adrese pe 16 biți și date pe 16 biți, pentru a acoperi adresele între 0x0000 și 0x03FF.

Vom folosi 2 chip-uri 1024x8b, unul pentru a stoca cei mai semnificativi 8 biți și altul pentru cei mai puțin semnificativi biți.

Împărțirea spațiului de adrese:

| A[15] | A[14] | A[13] | A[12] | A[11] | A[10] | A[9] | A[8] | A[7] | A[6] | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | Comentariu |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Prima adresă a grupului |

| 0 | 0 | 0 | 0 | 0 | 0 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Ultima adresă a grupului |

Condiția de chip-select (pentru ambele chip-uri) este !A[15] & !A[14] & !A[13] & !A[12] & !A[11] & !A[10].

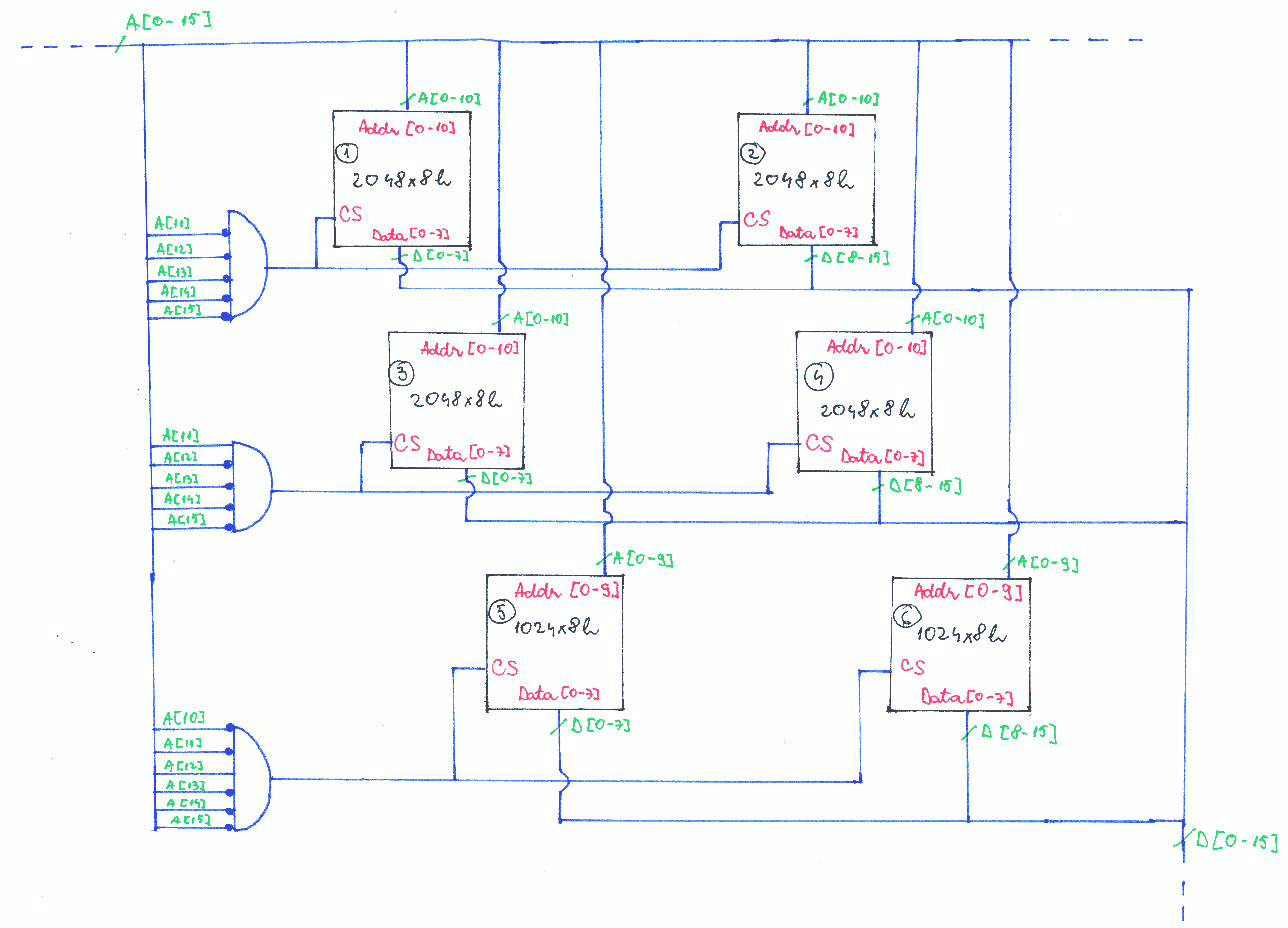

Exemplul 6

Task: Conectați o capacitate de stocare de 10kB ROM. Arhitectura calculatorului are bus de adrese și de date pe 16 biți. Aveți la dispoziție chip-uri 1024x8b și 2048x8b.

Capacitatea de 10kB înseamnă 5130 adrese a câte 2 bytes (16 biți) fiecare. Putem folosi 4 chip-uri 2048x8b și 2 chip-uri 1024x8b.

Facem din nou tabelul cu împărțirea spațiului de adrese:

| A[15] | A[14] | A[13] | A[12] | A[11] | A[10] | A[9] | A[8] | A[7] | A[6] | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] | Comentariu |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Adresa de început pentru 1-2 (2048x8b) |

| 0 | 0 | 0 | 0 | 0 | … | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Adresa de final pentru 1-2 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Adresa de început pentru 3-4 (2048x8b) |

| 0 | 0 | 0 | 0 | 1 | … | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Adresa de final pentru 3-4 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Adresa de început pentru 5-6 |

| 0 | 0 | 0 | 1 | 0 | 0 | … | … | … | … | … | … | … | … | … | … | |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | Adresa de final pentru 5-6 |

Pe baza tabelului deducem că:

- condiția de chip-select pentru 1-2 este

!A[15] & !A[14] & !A[13] & !A[12] & !A[11]. - condiția de chip-select pentru 3-4 este

!A[15] & !A[14] & !A[13] & !A[12] & A[11]. - condiția de chip-select pentru 5-6 este

!A[15] & !A[14] & !A[13] & A[12] & !A[11] & !A[10].

Detalii extra

Tipuri de chip-uri care pot fi doar citite de o placă de bază: ROM, PROM, EPROM.

Tipuri de chip-uri read-write: EEPROM, Flash, SRAM, DRAM. Aceste chip-uri au un pin în plus (numit Write-Enable, sau Read-Write, care indica daca se face o citire sau o scriere). Pinul de Write-Enable trebuie legat la semnalul corespunzător de pe magistrala de comunicație.